# D14-039

Ultra Low Voltage Read and High Efficiency Write Circuits for Resistive Random Access Memory in Low Power System

應用於低功耗系統之具超低電壓讀取與高效率 寫入之電阻式隨機存取記憶體

### 隊伍名稱

小鬼當家 / Lab Alone

#### 隊長

簡惇妃 清華大學電機工程研究所

#### 隊員

劉彥辰 清華大學電機工程研究所 林鉦峻 清華大學電機工程研究所

# 作品摘要

近年來,非揮發性記憶體被運用在大量的電子產品上,如:智慧型手機、數位相機、筆記型電腦。市場對於大容量、低成本、低耗能和高速度的記憶體需求愈來愈大,目前常見的快閃記憶體(NAND Flash Memory)其寫入速度慢且無法隨機存取,隨著製成衍進成奈米等級之後,快閃記憶體在微縮尺寸上面遇到了困難,因此有其必要開發新型的非揮發性記憶體。而電阻式記憶體(ReRAM)是相當具有潛力的非揮發性記憶體,其特色為低寫入功耗、小面積、以及具有邏輯製成相容性,可降低製作成本。

電阻式記憶體(ReRAM)在學術界被廣泛的研究,其使用材料以及操作原理有很多種,簡單來説,在ReRAM的兩端點施加電壓,可以改變ReRAM的阻值,達到存0存1的效果。目前普遍的ReRAM記憶細胞架構為一個電晶體和一個ReRAM的組合(1T1R),適合用在需要快速讀取和低供給電壓的內嵌式裝置應用上,特別是電池供給的裝置。隨著元件的微縮,ReRAM的阻值愈來愈高,且寫入時間和阻值的飄移量愈來愈大,造成高阻態和低阻態之間的R-ratio(RH/RL)縮小。除此之外,ReRAM的低阻態偏高,有助於增加寫入時跨在ReRAM上面的跨壓,如此一來,可以減少寫入的電壓,以及記憶細胞架構電晶體的大小。

## 因此ReRAM記憶體會面臨到兩個問題:

- 1. 因為ReRAM的低阻態偏高,且R-ratio變小,使得讀取的感測範圍(sensing margin)變小,進而造成讀取速度慢,並限制了記憶體的最低操作電壓。

- 2. 由於寫入時間的漂移,大寫入電流(IDC-SET)造成大量的能量消耗。

在此,我們提出兩個電路來解決上述遇到的兩種問題,分別是swing-sample-and-couple voltage mode sense amplifier (SSC-VSA)和self-boost-write-termination (SBWT) scheme。

我們所提出的SSC-VSA把參考電壓設計在特別的準位上面,經由電路運作後,能夠有效率的把  $\Delta$  VBLS\_MIN當作讀取感測範圍,使得使用率高達99%,因此能操作在更低的電壓以及擁有更快的讀取速度,其讀取速度可比傳統的電壓感測電路快1.7倍以上。

至於ReRAM的寫入方面,我們提出SBWT scheme,它是一個4T的 自動偵測寫入完成電路,當ReRAM set(HRS→LRS)成功時,大 寫入電流會使得BL電壓上升,啟動BL和SBWT之間的正向回饋機 制,切斷電流路徑,可節省99%以上的耗能。

我們以28奈米製程實作1Mb ReRAM記憶體晶片,在供給電壓等於0.85V及0.27V下,量測讀取速度分別為6.8ns和404.4ns。除此之外,我們也成功驗證寫入終止電路機制。

# 指導教授 張孟凡/清華大學電機工程學系

成功大學電機學士,美國賓州州立大學 電機碩士,交通大學電子博士,2006年 進入清華大學電機工程學系任教至今。 具備10年以上產業界經驗,任教至今曾獲得

國科會吳大猷先生紀念獎及中央研究院年輕學者研究著作獎。

## 研究領域

奈米與下世代記憶體電路設計,低功耗低電壓電路、3D-IC電路、憶阻器電路。

# 指導教授

# 林崇榮 / 清華大學電子工程研究所

清華大學電機學士、清華大學電機碩士、清華大學電機博士。1996年加入台灣積體電路公司研發部門,於2005年進入清華大學電電子工程學研究所任教至今。

## 研究領域

記憶體元件、功率元件、CMOS 元件。

## **Abstract**

In recent years, nonvolatile memory is popularly used on electronic products, such as smartphone, camera, and laptop. The market of large capacity, low cost, low power and high speed memory becomes larger and larger. Flash memory is the mainstream embedded memory. However, it cannot achieve high speed write operation and be randomly accessed. Furthermore, it is difficult to scale down flash memory into deep nanometer scale. Thus, developing new nonvolatile memories is necessary. Among these emerging nonvolatile memories, Resistive Random Access Memory (ReRAM) is one of the most promising candidates. It has attractive characteristics such as low write power, small area, and logic-process compatibility which can lower the manufacturing cost.

ReRAM is widely researched in academia. It has many kinds of materials and operation principles. In simple words, when we apply a voltage across the ReRAM, we can change the resistance of ReRAM to achieve the binary storage. Currently, the most common memory cell structure is one transistor and one ReRAM (1T1R), which is suitable for high speed and low supply voltage embedded applications, particularly for devices powered by batteries. As devices shrink, ReRAMs have higher cell resistance(R) and greater variations in write time and R, which reduces the R-ratio (RH/RL) between the high-R state (HRS, RH) and low-R state (LRS, RL). ReRAM also have a high RL, which enables a larger voltage drop across ReRAM to reduce write voltage and cell-switch (CS) size.

Thus, ReRAM memory macro designs suffer two major problems:

- 1. Small sensing margin (SM), limited read-VDDMIN, and slow TAC due to high-RL and small R-ratio.

- 2. Increase in energy due to large set DC-current (IDC-SET) resulting from wide set-time (TSET) distribution.

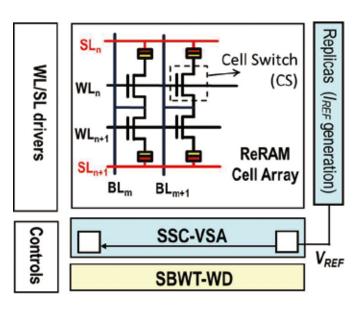

Here, we propose swing-sample-and-couple voltage mode sense amplifier (SSC-VSA) and self-boost-write-termination (SBWT) scheme to solve above two major problems, respectively.

Proposed SSC-VSA designs the VREF on specific voltage level, after the operations of the circuit, it can increase the usage of  $\Delta$  VBLS\_MIN (by up to 99%) as the SM for lower read VDDMIN and faster TAC. It can achieve 1.7x faster TAC across various VDD compared to conventional differential-input (CD) voltage mode sense amplifier.

As for ReRAM write operation, proposed SBWT scheme is a 4T self-detective write-termination circuit. When ReRAM successfully sets (HRS→LRS), large IDC-SET will increase the BL voltage, enabling the positive feedback between BL and SBWT and cutting off the current path, which can save over 99% write power.

We fabricated a 28nm 1Mb ReRAM memory macro. Under the 0.85V and 0.27V supply voltage, the measured read access times are 6.8ns and 404.4ns, respectively. Besides, the SBWT scheme has also been confirmed.

Fig.1 > Structure of ReRAM macro