# D15-012

Iterative Detection and Decoding Receiver for LDPC-Coded MIMO Systems

適用於 LDPC 編碼多天線系統的疊代式接 收器

# 作品摘要

### 研究動機:

行動裝置使用人口日益增加,無線資料傳輸需求也隨之提高。 多天線技術 (MIMO technology) 可增加資料傳輸量與提升資 料可靠度,已被現今通訊標準所採用。為了使傳輸資料達到 Shannon 極限,可使用 LDPC 編碼的 MIMO 系統搭配疊代式檢 測與解碼接收機(Iterative detection and decoding receiver, IDD receiver),然而疊代式接收機面臨高複雜度、運算時間過 長的設計挑戰,被認為未達實用階段,至今尚未被現有系統所 採用。本作品提出文獻上第一顆實現高速且低複雜度多天線系 統疊代式接收機,為通訊技術上之一大突破。

隊名 依西西

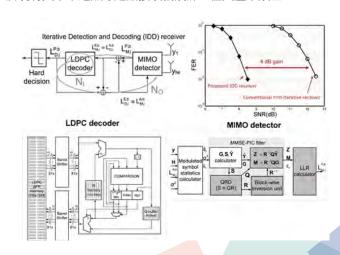

## 系統架構:

- 1. 傳統接收機在 MIMO 檢測器收到訊號後直接傳送至 LDPC 解碼器。疊代接收機設計為 MIMO 檢測器與 LDPC 解碼器 之間進行訊息疊代交換,以較可靠之接收訊息更正較不可 靠的訊息,可有效降低系統錯誤率。

- 2. 原本疊代式接收機在 MIMO 檢測器與 LDPC 解碼器之間來 回交換訊息,具有較低硬體使用率與較長運算時間。本作 品採用交錯解碼的排程,依序接收兩個碼框,分別運行在 MIMO 檢測器與 LDPC 解碼器,以此提升接收機吞吐量、 提高硬體使用效率和縮短運算時間,將硬體使用率提升至 100%。

- 3. 最佳的 MIMO 檢測器為 MAP (Maximum a posteriori) 檢 測器,但 MAP 複雜度太高,在硬體實現上幾乎可不行。 我們採用硬體複雜度較低之 MMSE-PIC 檢測器, 透過疊代 式解碼的更正錯誤能力,所實現的 MMSE-PIC 疊代式接收 機較 MAP 非疊代式接收機具有更好的錯誤率效能。

#### 硬體突破性:

1. MMSE-PIC 檢測器需要複雜之反矩陣計算,本作品使用可 擴充式之矩陣拆解演算法結合矩陣轉換,將其轉換為上三 角矩陣算用,並以低複雜度之 CORDIC 架構,只需要位移 器和加法器即可實現,省去硬體複雜度高的除法器,以達 成高速吞吐量。

- 2. 設計 MMSE-PIC 檢測器與 LDPC 解碼器資訊交換介面,本 作品改變資訊更新方式,從 LDPC 解碼器的後驗機率 (a posteriori probabilities, APPs) 記憶體提出資訊與 MMSE-PIC 檢測器的資訊運算,再存回後驗概率記憶體,節省原 本要傳給 LDPC 解碼器大量更新記憶體(31,104 位元), 以較少硬體複雜度達成相同錯誤率效能。

- 3. 本作品採用 MMSE-PIC 檢測器與 LDPC 解碼器外部資訊交 換之最佳疊代組合,具有最大邊際效能改善與最小額外增 加硬體複雜度,比非疊代式接收機有 1.6dB 增益, 玀輯閘 數為 998k。

#### 實作結果:

本作品提出之疊代式接收器以 40nm CMOS 製程實現,晶片面 積為 1.33 mm<sup>2</sup>, 最高工作頻率為 288 MHz。在 4x4 16-QAM 系 統可達到 794 Mb/s 的吞吐量。操作在 0.9V,晶片功耗為 135 mW,能量效率為 170 pJ/bit。本作品提出之疊代式接收器錯誤 率效能超越最佳非疊代式接收器,能量與面積效能甚至高於現 有之非疊代式接收器,所提之硬體架構與設計方法可直接應用 於現有與未來之無線通訊接收機設計,極具產業效益。

圖 1 / 疊代式接收機系統方塊圖、設計圖與錯誤率效能

# 指導教授 翁詠禄 / 清華大學電機工程學系、通訊工程研究所

1997 年畢業於臺灣大學電機工程學系,並於 2001 年在同系獲得博士學位。畢業後於工業界從事 藍芽和 PHS 基頻晶片研發 4 年,現任教於清華大學。近五年以第一或通訊作者的 IEEE 期刊論文 有 16 篇。很榮幸獲頒 101 以及 102 清華大學產學合作績優獎項。

## 研究領域

編碼理論、無線通訊系統以及通訊 IC 設計。

## 指導教授 楊家驤/交通大學電子工程學系

楊家驤教授於 2002、2004 年畢業於臺灣大學電機工程學系與電子工程學研究所,並於 2010 年 獲得加州大學洛杉磯分校電機博士學位,隨後在加州大學洛杉磯分校擔任博士後研究,在 2011 年加入交通大學電子工程學系任教至今。

## 研究領域

生醫訊號處理與晶片設計、通訊系統與積體電路設計、低能耗電路。

# **A** bstract

#### Motivation

In order to handle more mobile users, there is a strong demand for high-speed wireless communication systems. Multi-input multi-output (MIMO) technology has been widely adopted to support higher speed and more reliable data transmission. A low-density parity-check (LDPC)-coded MIMO system with iterative detection and decoding (IDD) receiver can achieve near-capacity performance. A practical IDD receiver, however, is still regarded infeasible due to its prohibitively high computational complexity and lengthy latency. In this work, we propose the first true IDD receiver with an MMSE (minimum mean-square error) based MIMO detector and a LDPC decoder to support high throughput with minimized area. Compared with conventional receiver, this work has better FER (frame error rate) performance, the optimal area efficiency and energy efficiency.

## System model

- For conventional non-IDD receiver, the decoder outputs the information bits without feeding the soft information back to detector. In an IDD receiver, in contrast, a MIMO detector and LDPC decoder iteratively exchange soft messages represented by the log-likelihood ratio (LLR) for each code bit.

- IDD receiver is hard to implement due to high computational complexity and length latency. In our design, an efficient interface scheduling is proposed. The hardware utilization can be improved by 2 interleaved frames that yield 100% utilization with a minimized latency.

- 3. The optimal MIMO detector such as MAP (maximum a posteriori) detector is regarded infeasible as a result of high computational complexity. An MMSE-PIC (parallel interference cancellation) based IDD receiver can achieve the better FER performance than MAP based conventional receiver. This demonstrates a low-complexity MMSE-PIC detector is sufficient for IDD receiver, which can be leveraged to reduce detector complexity, especially for large-scale MIMO systems.

### Breakthrough

- MMSE-PIC detector needs to process inverse matrix operation that reduces the hardware throughput. To enhance the throughput with minimized area, QR decomposition (QRD) is utilized to facilitate matrix inversion needed in the MMSE-PIC algorithm by leveraging the characteristic of the upper-triangular matrix.

- 2. The messages are updated based on the turbo principle for IDD. In the direct-mapped design, the LDPC decoder requires an additional memory for LDPC intrinsic memory to store the LLR difference. In the work, an efficient interface is proposed to reduce hardware complexity. The messages are updated only when the detector produces the LLR difference, saving 31,104 bits for memory storage.

- 3. Based on the tradeoff between hardware complexity and FER performance, Outer iteration and inner iteration can be determined through sensitivity analysis. In this work, outer iteration and inner iteration are equal to 3 respectively that is adopted to achieve the optimal operation, where a gain of 1.6 dB over the base-line MMSE-PIC non-IDD receiver is achieved.

## **Experimental Results and Conclusion**

A LDPC-coded MIMO systems with IDD chip is integrated in 1.33mm<sup>2</sup> in 40nm CMOS. The maximum gross throughput is 794Mb/s for a 4x4 16-QAM configuration at 288MHz. The chip dissipates 135mW at 0.9V, achieving an energy efficiency of 170pJ/bit. The proposed MIMO detector, LDPC decoder, message exchange interface, and outer-inner loop optimization for the IDD receiver can be applied to existing and future communication systems to enhance transmission performance.