適用於多模式三維晶片解碼系統 之溫度與效能感知映射演算法與 架構設計

Thermal-Aware Kernel and Memory Mapping Architecture Design for Three-Dimensional Multi-Mode Channel Decoding Systems 隊伍名稱 元智大學一可靠數位系統實驗室/ YZU-RDS Lab

隊 長 林浩德 / 元智大學電機工程研究所 隊 員 蘇河雲 / 元智大學電機工程研究所

指導教授 林書彦/元智大學電機工程學系

## 作品摘要

隨著三維晶片製造技術的進步,未來的晶片設計將透過三維晶片堆疊,以實現記憶體與不同功能晶片之間的異質整合。在高效能無線通訊設備中,會搭配前饋式錯誤更正碼技術(Forward Error Correction, FEC)來降低訊號出錯率,提高傳輸品質。前饋式錯誤更正碼常具備一種以上的解碼模式,以支援不同的通訊協定。雙模式前饋式錯誤更正碼之三維架構,此一硬體架構同時支援兩種錯誤更正碼,並藉由三維組片的優勢,提高傳輸頻寬。本設計中,透過兩種錯誤更正碼解碼模式下所需記憶體需求,探索對應之區塊式記憶體架構(block-based memory architecture);並透過兩種模式下的溫度差距,開發可用於雙模式解碼核心與區塊式記憶體三維晶片架構之溫度控管映射演算法與架構設計,提供不同解碼模式下,三維架構所需要記憶體需求,並透過溫度控管映射演算法解決三維晶片堆疊所帶來過熱問題。

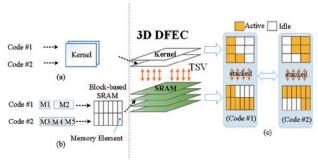

本設計應用之錯誤更正碼系統為同時堆疊多模式前饋式錯誤 更正碼與區塊式記憶體之三維架構。其中錯誤更正碼解碼核 心晶片支援同時支援兩種錯誤更正碼,如圖一 (a);堆疊的記 憶體晶片為區塊式記憶體架構,如圖一 (b),並透過三維晶 片堆疊技術形成三維架構,如圖一 (c)所示。

圖 1. (a) 兩種模式前饋式錯誤更正碼運算核心, (b) 區塊式記憶體架構, (c) 兩種模式前饋式錯誤更正碼三維架構之示意圖

## **Abstract**

In modern wireless communication standards, such as LTE and WiMAX, the turbo code and low-density parity-check (LDPC) code are applied because of the excellent ability in forward error correction (FEC). To support multiple standards in a chip, many dual-mode forward error correction (DFEC) designs have been proposed to support turbo and LDPC decoding. In this work, the thermal-managed three-dimensional dual-mode forward error correction (3D DFEC) architecture is proposed. In 3D DFEC, the reconfigurable block-based SRAM architecture can support the memory requirement in different active DFEC kernels and the decoding modes. The thermal issue can be solved by the proposed thermal-aware mappings.

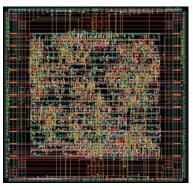

圖 2. 溫度控管映射控制器之 晶片佈局圖

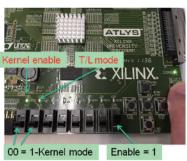

圖 3. 溫度控管映射控制器之 Xilinx FPGA 驗證圖