# D21-039

具有溫度補償快速導通技術的積體化氮 化鎵矽基板閘極驅動器和氮化鎵開關以 提升可靠度

Fully Integrated GaN-on-Silicon Gate

Driver and GaN Switch with Temperaturecompensated Fast Turn-on Technique for

Improving Reliability

隊伍名稱

**史密提威威傑格曼傑森** Smitty Werben Jaggar Man Jensen

隊長

高郁詠

陽明交通大學電控工程研究所

隊員

林書永

陽明交通大學電機工程研究所

黃 飛

陽明交通大學電機工程研究所

羅愉鈞

陽明交通大學人工智慧技術與應用碩士學位學程

# 作品摘要

由於氮化鎵(GaN)相對於傳統的矽(Si)電晶體有許多優勢,使用GaN的電源轉換器已迅速增加。650V增強型氮化鎵(eGaN)高電子移動率電晶體(HEMT)具有以下優點:1.可承受高壓應力 2.低寄生電容 3.低導通電阻(R<sub>ON</sub>) 4.無反向恢復電荷損失。GaN功率電晶體可以實現高頻開關操作,並優化電路的功率密度和尺寸。使用GaN的電源轉換器有許多優點,例如高效率及高功率密度,因此GaNHEMT可突破傳統使用矽製程功率轉換器的操作頻率與效能,並有機會成為下一世代功率元件的主要材料。

GaN HEMT的熱門應用之一為用於5G通訊系統的封包追 蹤電源調變器 (ETSM)。由於5G系統中的ETSM模組需要 達到將近100MHz的高工作頻率及低開關損耗以優化整體 效率,因此使用低寄生效應的GaN HEMT作為功率開關成 為熱門的解決方案,也使GaN HEMT的閘極驅動器逐漸成 為熱門的研究主題。

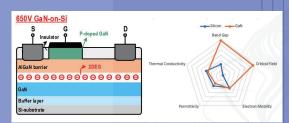

650V GaN-on-Si的結構如圖一所示。近年來,GaN製程中已經開發出具帶有帶負電載子(電子)的N型通道的元件,且已開發出常態關閉型「增強模式」eGaN及易於實現的常態開啟型「空乏模式」dGaN。目前常用的GaN製程包括用於低壓電路設計的12V eGaN元件和用於電源開關的 650V eGaN元件。這兩種元件間的區別在於650V eGaN元件的汲極和源極的間距更長,因此可承受高電壓應力。由於eGaN的通道由2DEG組成,其具有比傳統CMOS製程更優異的電子移動率,因此GaN可以用更小的體積實現與傳統CMOS製程相同性能,也更具競爭優勢。

儘管GaN有許多的優點,但其仍存在製程缺陷,從而導致可靠度問題。例如2DEG層容易受溫度影響,導致元件溫度過高而損毀。GaN的緩衝層和Si基底之間存在嚴重的異質缺陷,使導熱性差、基底強度薄弱。在溫度影響下,將加劇熱載子的注入(hot carrier injection)和捕捉效應(trapping effects),並且GaN HEMT中的2DEG層將隨著時間的流逝而減弱,因此650V GaN HEMT的導通電阻( $R_{\text{ON}}$ )和閾值電壓( $V_{\text{TH,E}}$ )將逐漸增加,從而降低GaN元件的可靠度。

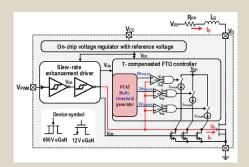

因此,本作提出全積體化的GaN-on-Si間極驅動器和GaN開關,其中包含T-compensated FTO控制迴路可以減輕溫度的影響。此外,串聯反相器中的電壓迴轉率增強技術可以產生足夠高的控制電壓  $(V_{ON})$  以實現快速導通,並在T-compensated FTO技術開始之前提供足夠的 $I_G$ 來為 $V_G$  充電。由於實現GOMD = 100 位因,因此的穩壓器可以為內部電路提供足夠且穩定的內部電壓。另外,所提出的控制器可以正確追蹤米勒平台電壓,從而將開關頻率提升到GOMD = 100 位犯轉率可以達到GOMD = 100 位犯轉率可以達到GOMD = 100 位犯轉率可以

▲圖一氮化鎵製成的結構及優勢

## 陳科宏 陽明交通大學電機工程學系

臺灣大學電機工程學士、碩士、博士,現為陽明交通大學電機工程學系教授。曾於1996至1998年任臺北飛利浦公司兼職IC設計人員,1998至2000年任Avanti擔任項目經理,從事電源管理IC的設計。成立陽明交通大學混合信號和電源管理IC實驗室,在IEEE頂尖期刊(JSSC及TPE)和會議(ISSCC及VLSI symposium)上有卓越的貢獻,並擁有多項專利。

### 研究領域

電源管理積體電路設計、混合訊號電路設計、液晶顯示器(LCD)驅動器設計、氮化鎵驅動器設計 動器設計

#### **Abstract**

Recently, due to the inherent advantages of gallium nitride (GaN) over traditional silicon (Si) transistors, power converters based on GaN has rapidly increased. For example, 650V enhancement mode GaN (eGaN) high electron mobility transistor (HEMT) has the following advantages: (1) high voltage stress. (2) low parasitic capacitance. (3) low on-resistance ( $R_{\text{ON}}$ ). (4) no reverse recovery charge loss. Thus, high switching operation by the GaN switches can provide high power density and compact size solution.

However, migrating the design of power converters from Si-based to GaN-based will bring many improvements, which require consideration of all components in the system. This consideration has led to the growth of the power converter design ecosystem that supports GaNbased designs. GaN-based power converters have many advantages, such as high efficiency, high power density, and the cost of converters is lower than that of siliconbased power converters. The characteristics of GaN HEMTs have started to renew the development of power converter, which is enabling higher switching frequency operation and higher transfer power density than the previous slower switching, bulkier silicon processes. For example, one of the applications using GaN HEMTs is the envelope tracking supply modulator (ETSM) system. Because in the field of 5G, the ETSM system needs to achieve an operating frequency close to 100MHz to optimize the overall efficiency. Using integrated GaN driver and GaN switch can break through the limitations of traditional silicon process. In these applications, GaN HEMTs are used to complete the entire system of gate driver with GaN switch and has recently become more and more competitive.

However, today's GaN HEMT has serious process defects, especially depending on the selected substrate. Thus, under temperature influences, they will seriously aggravate the hot carrier injection and trapping effects, and the two-dimensional electron gas (2DEG) layer in the GaN HEMT will weaken over time. The  $R_{\text{ON}}$  and threshold voltage (V $_{\text{TH,E}}$ ) of 650V GaN HEMT gradually increase to rapidly decline the reliability.

The project proposes a fully integrated GaN-on-Silicon gate driver and GaN switch. First, the temperaturecompensated fast turn-on technique (T-compensated FTO) control loop can alleviate the temperature effect. Besides, the slew rate enhancement technique in the cascaded inverters can generate a sufficiently high control voltage (V<sub>ON</sub>) to achieve fast turn-on and provide enough I<sub>G</sub> to charge the V<sub>G</sub> before T-compensated FTO technique starts. Second, the proposed regulator can provide a high and stable internal voltage for internal circuits because of the low-frequency gain of 60 dB and phase margin of 64 degrees can be guaranteed. Furthermore, the Miller plateau voltage can be tracked correctly by the proposed controller so that the switching frequency can be raised up to 50MHz and the dV<sub>DS</sub>/dt slew rate can reach 118.3V/ns for high efficiency and high switching operation.

▲ Fig. 2 Proposed fully integrated GaN driver structure