# D21-074

適用於毫米波 W 頻段具高解析度與多用戶 抗干擾之雷達系統

A Millimeter-Wave W-Band High-Resolution Multi-User Interference-Tolerant Radar System

隊伍名稱

好多雷也不驚

Fearless Radar

隊長

蔣靜雯

陽明交通大學國際半導體產業學院

隊員

梁嘉仁

陽明交通大學電子工程研究所

李佑荃

陽明交通大學電子工程研究所 沙畢瑞 Shabirahmed B. Jigalur 陽明交通大學國際半導體產業學院

# 作品摘要

CMOS毫米波雷達能克服惡劣天氣條件,且其高集成度在大規模生產上可帶來極佳的成本效益。與現有的K頻段和E頻段雷達相比,W頻段雷達可提供更大的信號頻寬,從而提高距離解析度。一般而言,在涉及多車輛的自動駕駛應用中,來自相鄰車輛的雷達信號不可避免地會互相產生干擾,這可能會對雷達的功能和準確性造成不利的影響。因此,減輕互相干擾是多使用者雷達系統的一個必備功能。

有鑑於此,本計畫開發了一個W頻段88.5-93.5GHz具多用戶抗干擾功能之雷達系統。此系統結合EHC(Extended Hyperbolic Congruential)碼與Robert L. Frank所提出之多相碼,又稱Frank碼,形成EHC-Frank碼來作為雷達信號。Frank碼具有高自相關(auto-correlation)與低交互相關(cross-correlation)特性。而交互相關可藉由EHC碼的一次碰撞特性更進一步降低,達到同時支持多個使用者,並具抗干擾的功能。本計畫之EHC-Frank碼的長度為1369。

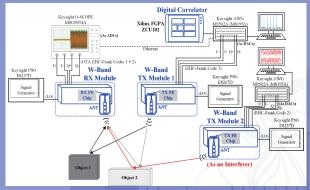

圖一顯示了本作品的展示架構圖。本作品包含兩個W頻段發射機(TX)模組(其中第2個模組為干擾源)、一個W頻段接收機(RX)模組、以及一個在FPGA實現的數位相關器(digital correlator)。TX/RX模組包含TX/RX前端[front-end(FE)]晶片與天線(ANT)。數位相關器執行EHC-Frank碼之交互相關運算,藉由外接之任意波形產生器(AWG)[作為數位類比轉換器(DACs)]、示波器(O-SCOPE)[作為類比數位轉換器(ADCs)]、以及信號產生器(PSG)[作為本地振盪器(LO)]等儀器,形成一個完整的W頻段雷達系統。

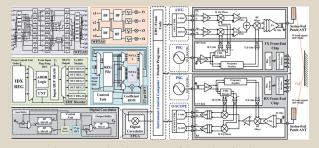

此TX與RX前端晶片採用超外差架構,以達到此雷達系統所需的鏡像抑制和LO隔離度。其中TX前端晶片提供7.1dBm的輸出功率,而RX前端晶片達到10dB的雜訊指數

(NF) 和-12dBm的1dB壓縮點( $P_{1dB}$ )。TX/RX前端晶片以28-nm CMOS製程實現,包括墊片(pads)的面積為1.44/1.31mm²。在0.9V操作電壓下,TX/RX前端晶片消耗功率為145/128mW。此外,1x3串饋貼片天線(series-fed patch antenna)以RO4003C高速電路板實現。藉由FR4電路板為基板,透過打線鍵合的方式和TX/RX前端晶片整合,可產生具有成本效益的W頻段TX/RX模組,以進行無線空中(OTA)驗證。

由時域相關運算和Frank碼的數學公式推導可得: 1369點 EHC-Frank碼時域相關運算等於37次37點離散傅立葉轉換(DFT)的加總。其中37點DFT藉由Rader's演算法,可拆解為直流值與36點循環摺積運算;而36點循環摺積以36點DFT、點乘、以及36點反離散傅立葉轉換(IDFT)完成。其中36點DFT藉由4點與9點Winograd傅立葉轉換演算法高效率完成,36點IDFT則重複使用36點DFT硬體。此數位相關器已實現在Xilinx ZCU102 FPGA硬體平台上,執行速度在單路架構上可達138MHz。經OTA測試,在5GHz的信號頻寬下,本計畫之雷達系統可提供3cm的距離解析度。

▲ 圖一 W頻段高解析度暨多用戶抗干擾雷達系統

### 管延城 陽明交通大學國際半導體產業學院

美國加州大學洛杉磯分校電機工程博士,現為陽明交通大學國際半導體產業學院副教授。 曾任美國休斯研究實驗室研究員與技術領導。

#### 研究領域

毫米波通訊和雷達電路與系統設計

## 劉志尉 陽明交通大學電子工程學系

清華大學電機工程博士,現為陽明交通大學電子工程學系教授、工業技術研究 院合聘教授。曾任工業技術研究院系統晶片技術發展中心副理。

#### 研究領域

系統晶片設計、訊號處理、數位通訊、編碼理論

#### **Abstract**

This project presents a W-band (88.5-93.5-GHz) radar system that can reduce the radar interferences from multiple users operating simultaneously by combing an Extended Hyperbolic Congruential (EHC) code and a polyphase code proposed by Robert L. Frank (also known as Frank code) to construct a 1369-point EHC-Frank code as a radar waveform for each user. The proposed EHC-Frank code is obtained by applying the one-coincidence feature of the EHC code to make the Frank code, which exhibits high auto-correlation and low cross-correlation, feature even lower cross-correlation, thus achieving the functionality of multi-user interference tolerance.

This radar system (see Fig. 2) includes a W-band transmitter (TX) module, a W-band receiver (RX) module, and a digital correlator implemented on an FPGA platform. The TX/RX module contains a TX/RX front-end chip and an antenna (ANT). The digital correlator performs the cross-correlation for the EHC-Frank code. A complete W-band radar system is formed by integrating the W-band TX and RX modules, the digital-correlator FPGA platform, the instruments including an arbitrary waveform generator (AWG) [acting as digital-to-analog converters (DACs)], an oscilloscope (O-SCOPE) [acting as analog-to-digital converters (ADCs)], and two signal generators (PSGs) [acting as local oscillators (LOs)], and an instrument-control computer.

The TX/RX front-end chip adopts a superheterodyne architecture to achieve the image rejection ratio and LO isolation level required by this radar system. The TX front-end chip provides a 7.1-dBm output power, and the RX front-end chip achieves a 10-dB noise figure and a -12-dBm P1dB. The TX/RX front-end chip is realized in a 28-nm CMOS process, and

its pad-included area is 1.44/1.31mm2. Under a 0.9-V supply, the TX/RX front-end chip consumes 145/128mW. Moreover, the TX/RX antenna based on a 1x3 series-fed patch architecture is implemented on a Rogers RO4003C high-speed PCB. The TX/RX antenna is integrated with the TX/RX front-end chip on an FR4 PCB through a wire-bonding technology to form the cost-effective W-band TX/RX module for over-the-air (OTA) verifications.

It can be derived mathematically that the time-domain correlation for the 1369-point EHC-Frank code equals the summation of 37 37-point discrete Fourier transforms (DFTs). Through Rader's algorithm, the 37-point DFT can be decomposed into a zero-frequency component and a 36-point circular convolution, which can be realized through a 36-point DFT, pointwise multiplication, and a 36-point inverse DFT (IDFT). Moreover, the 36-point DFT can be realized efficiently through the 4-point and 9-point Winograd Fourier transform algorithms. The 36-point IDFT is realized by reusing the 36-point DFT hardware. This digital correlator is implemented in a single-stream architecture manner on a Xilinx ZCU102 FPGA platform operating at 138MHz. The OTA experimental results show that this radar system can achieve a distance resolution of 3cm with a 5-GHz signal bandwidth.

▲ Fig. 2 The proposed architectures of the W-band radar system, TX and RX front-end chips, and FPGA-based digital correlator