# 13th GOLDEN SILICON AWARDS

D13-057

A 0.57nJ/Pixel Video-**Recording SoC**

超低耗能影像錄製系統晶片設計

隊伍名稱

宅男奇普仕 / Otaku Chips

隊長

中正大學資訊工程研究所 簡呈安

隊員

中正大學電機工程研究所 張耿瑞 中正大學電機工程研究所 張倍耀 交通大學資訊工程研究所 余永暉

## 作品摘要

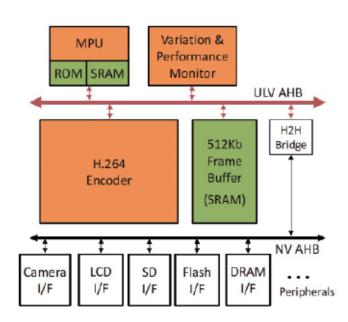

本次參賽作品為超低耗能多媒體影像錄製SoC(System on Chip) 設計,使用TSMC 65nm低功耗CMOS製程技術進行設計與製作。 本作品整合一低功耗、低頻寬、高效能H.264視訊編碼器與一超 低功耗微處理器 (MPU) 設計,並搭載時脈最佳化之ROM模組、超 低電壓 (Ultra-low-voltage, ULV) 技術之8T SRAM 模組、超低電壓 512Kb影像暫存緩衝器 (frame buffer, FB) 以及所有必要之SoC系 統周邊,如外部SDR記憶體控制器、SD card控制器、LCD顯示控制 器、ANT+網路傳輸介面以及攝影機影像擷取控制介面等,如圖一 所示。本作品並使用ULV 元件資料庫來進行超低耗能多媒體SoC 系統之實作,同時使用客製化之Pulsed D flip-flop來達到廣範圍 (wide-range) 電壓調整,同時減少低電壓時之製程變異影響,並 採用timing和leakage同步最佳化的ROM/SRAM以及先進的功率管 理(Advanced energy management, AEM)技術。結合上述技術, 本作品可以在電壓1V時達到以H.264錄製HD720 32fps視訊,同時也 可以降壓到0.5V時達到錄製H.264 QQVGA 30fps,並降低其耗能到 0.57nJ/pixel之超低耗能表現,如圖二所示。

本作品為全球第一顆低電壓低耗能影像錄製SoC,並整合多種功能 模組在單一系統晶片上,同時以超低電壓電路技術加以實現,讓 超低電壓電路設計技術能夠有機會落實於產品上。本作品所提出 之超低耗能SoC系統晶片可以應用在無法長時間供電之手持式裝 置上,如自行車行車記錄器、鈕扣型錄影機、項鍊式錄影機等,並 可以搭配ANT+無線傳輸介面,將經過縮小之畫面同步傳輸到手 機或平板裝置上觀看。同時本作品也可以應用於鈕釦型隨身影像 紀錄上,因為它可以操作在超低電壓下,有效降低耗能,可以長時 間拍攝個人隨身紀錄來編寫個人日記等。總之,本作品所提出之 超低耗能影像錄製系統晶片設計不僅具有學術價值,同時更具有 潛在之產業應用性,讓超低電壓低耗能系統晶片技術可以有機會 進行產業化,創造可觀之產業效益。

圖1 > Block diagram of ULV video recording SoC

### 指導教授

#### 郭峻因 / 交通大學電子工程學系及電子研究所

1985-1993 年取得交通大學電子研究所博士。目前擔任交通大學電子工程學系教授兼電子研究所所長(2012/8-迄今),並同時擔任智慧電子國家型計畫分項召集人(2011/1-迄今)。1996-1999 年曾任聯合技術學院電子工程系系主任,並陸續擔任旺宏電子(1996-1999 年)、唯典科技(2000-2004 年)、凌華科技(2002-2004 年)顧問一職。2005-2008 年,擔任中正大學 SoC 研究中心主任,2009-2011 年為中正大學特聘教授兼系主任。

#### 研究領域

VLSI Design, Digital Signal Processing, Digital IP and SoC Design, Intelligent Vision Processing System.

#### 王進賢 / 中正大學電機工程學系

1988年取得交通大學電子研究所博士。2009年迄今擔任中正大學電機工程學系特聘教授。1988-1991年擔任工研院電腦與通訊工業研究所應用電子部課長,1991-1995年擔任工研院電腦與通訊工業研究所積體電路設計部經理,1995年轉任中正大學電機工程學系任教迄今,期間同時擔任中正大學晶片系統研究中心主任(2003-2005)、中正大學電機工程學系系主任(2006-2009)、國科會 NSoC 計畫召集人(2010-2011)、國科會微電子學門召集人(2009-2011)。

#### 研究領域

晶片系統設計、低電壓低功率積體電路設計。

#### **Abstract**

This work presents an energy-efficient video recording SoC fabricated in TSMC 65nm LP CMOS technology, which integrates a complexity-&bandwidth-efficient H.264 video encoder, an ultra-low-power (ULP) MPU with timing-optimized ROM & 8T SRAM macros for ultra-low voltage (ULV) operations, a 512Kb ULV & leakage-aware 8T SRAM for the frame buffer (FB), and various on-chip peripherals, as shown in Fig. 1. By utilizing both a ULV cell libraries with custom pulsed D flip-flops (PFF) for wide-range voltage scaling and ROM/SRAM macros optimized simultaneously for timing & leakage, as well as an advanced energy management (AEM), the proposed SoC achieves 32fps HD720 H.264 real-time encoding at 1.0V, and reaches as low as 0.57nJ/pixel ultra-low-energy dissipation when doing 30fps QQVGA H.264 video encoding, as shown in Fig. 2.

The proposed SoC is the first ultra low voltage video recording SoC published in the world. The proposed SoC also integrates a variety of functional modules into one single chip to support the real-time video recording functions. Based on the proposed design, we can implement the some innovative commercial products with the low power consumption, like bike recorders, button recorders, and necklace recorders. Moreover, the proposed SoC can also encode the down-sampled video and transmit it through the ANT+ interface to smart phones or tablets for remote display. There will be lots of innovative applications coming from the proposed ultra low voltage

video recording SoC. For example, by equiping the proposed SoC in the button recorder, we can use it to record everything in our daily life to serve as the personal diary. In summary, the proposed ultra low voltage video recording SoC exhibiting the excellent low-power performance can enable many intelligent video applications in the near future.

Fig.2 > ULV system prototype demo