# D14-088

High Throughput Video Code 高吞吐率視訊壓縮編碼器

### 隊伍名稱

無線超高畫質視訊傳輸精靈 / Wireless Ultra High Definition Video Transfer Wizard

## 隊長

陳益國 元智大學電機工程研究所

#### 隊員

游奕倫 元智大學電機工程研究所

# 作品摘要

無線高畫質傳輸應用的便利性已經在周遭的生活上開始發酵,這一點由兩個例子可以清楚看出,如圖1為2013年無線高畫質傳輸最新應用發展,第一點如圖1 (a) 所示,可以清楚觀察到Wii U已經從前一代的主機Wii,把畫面解析度從480p(720 x 480)提升至Full-HD 1080p(1920 x 1080)的水準,並配合Wii U Game Pad將畫面資經由無線傳輸的方式接收主機的顯示資訊,而此時,電視的資訊就可已觀賞其它頻道資訊,並不需要顯示遊戲畫面內容,如此可大幅增加使用的彈性。第二點如圖1(b)所示,目前Samsung所推出的智慧型電視(Smart TV)有一很重要的功能「All Share」,主要將智慧型手機(Smart Phone)或是

平版電腦(PAD)的畫面資訊分享到電視上,藉由大螢幕呈現的高畫質影像來分享,而後者,亦可以將電視顯示資訊傳送到智慧型手機或是平版電腦來顯示,讓使用者可以不受空間的限制,不間斷的享受當下所收看的節目,在配合目前智慧型手機和平版電腦的面板解析度也來到了Full-HD 1080p規格,由此發展趨勢可知,高畫質顯示資訊,不在只有家用的LED TV能夠獨佔,而是透過無線高畫質傳輸技術,可以讓使用者具有更彈性及更便利的視覺享受。

由前段敘述可以得知,無線高畫質傳輸應用已經出現在目前日常生活中,並且帶來極大的便利性,但是對於超高畫質8K4K的應用,卻還有其技術限制之處,而本作品的主要目的是將超高畫質8K4K的畫面壓縮,之後再進行傳送,藉由壓縮把傳輸資料量降低到目前無線高畫質傳輸能夠處理的頻寬。

這次作品預計支援畫面解析度包含了基本的Full-HD 1080p,次世代高畫質4K2K及超高畫質8K4K,由上述對於超高畫質8K4K的預估傳輸率高達約47 Gbps,如此龐大的視訊資料,若要用一般genral purpose的影像/視訊壓縮演算法來處理,如JPEG、JPEG-2000、H.264/AVC,High Efficiency Video Coding(HEVC,H.265)等,在處理速度及在硬體成本上會有其限制之處,因此本作品的壓縮目的並不是以有限的儲存空間為主,例如VCD、DVD及Blu-ray Disc等,因此壓縮倍率並不需要到幾十到幾百倍,最主要是要讓高畫質的畫面透過本作品的技術,也能夠透過現今的無線高畫質傳輸相關標準中呈現。

(a) Wii U Game Pad

(b) Smart TV

圖1 > 2013年之無線高傳輸應用發展(資料來源:a. http://www. nintendo.com/wiiu/features/;b. http://www.samsung. com/tw/consumer/televisions/televisions/smart-tv/ UA75F8000AMXZW-features#mou03)

## 指導教授

# 李宇軒/元智大學電機工程系

中央大學電機工程博士。擔任元智大學電機工程學系助理教授(2010年8月迄今)。

## 研究領域

視訊處理、視訊壓縮、影像處理演算法及晶片架構設計。

## **Abstract**

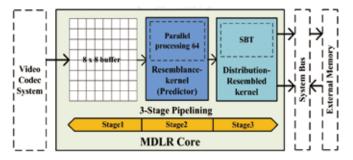

The hardware architecture of proposed lossless frame recompression algorithm is illustrated in Fig. 2 This hardware architecture is designed with 3-stage pipelining. The first stage is allocated to a 8 X 8 buffer storing an entire 8 X 8 block for following encoding procedure. The second stage performs prediction for every pixel in the 8 X 8 block with parallel processing. The third stage converts all residuals from second stage to SBT codewords. A 8 X 8 block is a basic processing unit in this data scheduling. At first, 64 pixels in a 8 X 8 block are sequentially stored into the 8 X 8 buffer. After 64 cycles, the 8 X 8 buffer is fullyloaded. The prediction mode of each pixel can be accomplished within a single cycle, since all pixels in a 8 X 8 block are already available. After one cycle, 63 residuals are generated, and each one is sequentially converted to a SBT codeword by SBT coding engine. After 63 cycles, the SBT coding engine can generate 63 SBT codewords. Meanwhile, the 64 pixels of next 8 X 8 block are also sequentially stored into the 8 X 8 buffer. Note that the prediction engine is designed with parallel processing to perform the predictions of 64 pixels within a single cycle. This data path organization can greatly save encoding latency. If the prediction engine is designed with sequential processing, it consumes 64 times the latency of parallel processing.

Fig.2 > Hardware architecture of RDLR core